- 您现在的位置:买卖IC网 > Sheet目录2008 > MAX1249AEPE+ (Maxim Integrated Products)IC ADC 10BIT SERIAL 16-DIP

MAX1248/MAX1249

+2.7V to +5.25V, Low-Power, 4-Channel,

Serial 10-Bit ADCs in QSOP-16

______________________________________________________________________________________

11

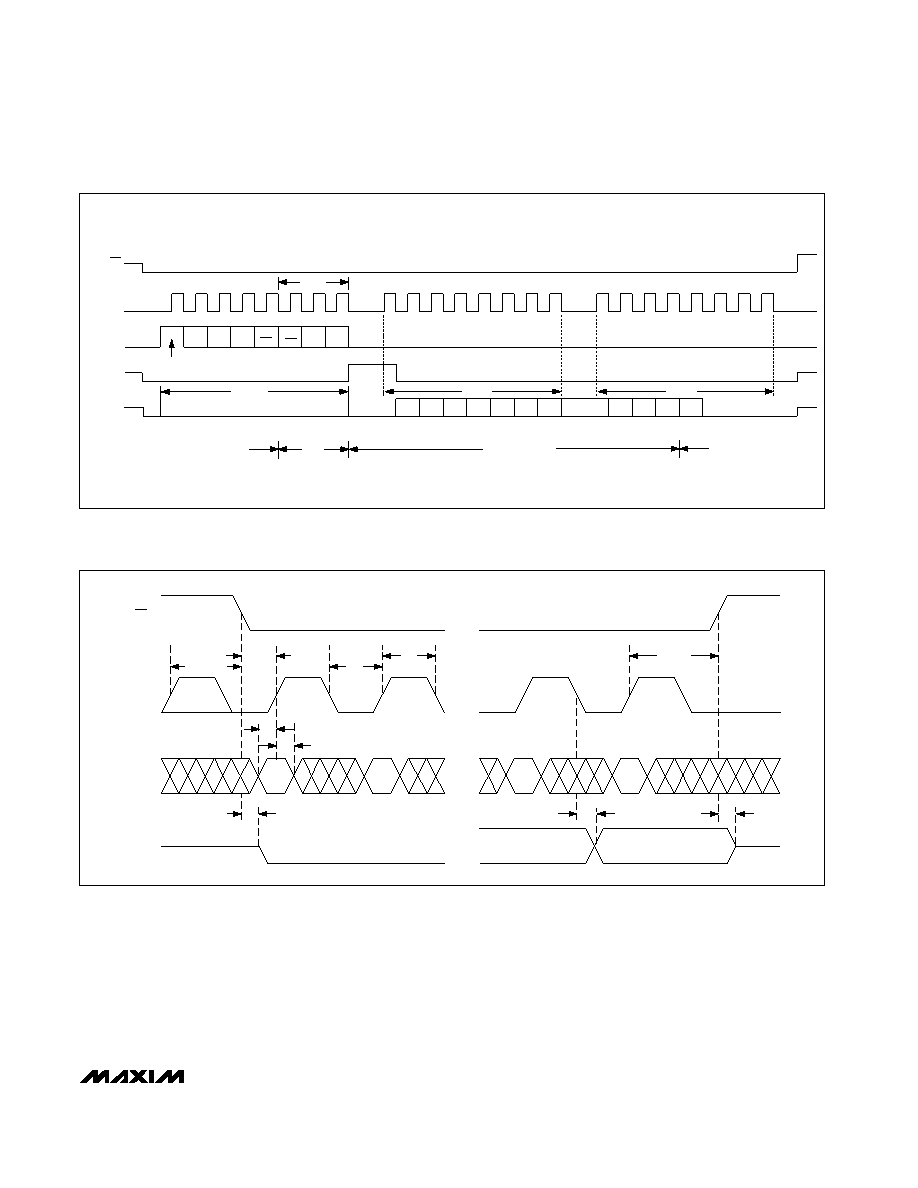

CS goes high; after the next CS falling edge, SSTRB will

output a logic low. Figure 7 shows the SSTRB timing in

external clock mode.

The conversion must complete in some minimum time,

or droop on the sample-and-hold capacitors may

degrade conversion results. Use internal clock mode if

the serial-clock frequency is less than 100kHz, or if

serial-clock interruptions could cause the conversion

interval to exceed 120s.

CS

SCLK

DIN

DOUT

tCSH

tCSS

tCL

tDS

tDH

tDV

tCH

tDO

tTR

tCSH

Figure 6. Detailed Serial-Interface Timing

SSTRB

CS

SCLK

DIN

DOUT

1

4

8

12

16

20

24

START

SEL2 SEL1 SEL0

UNI/

BIP

SGL/

DIF

PD1 PD0

B9

MSB

B8

B7

B6

B5

B4

B3

B2

B1

B0

LSB

S1

S0

ACQUISITION

(fCLK = 2MHz)

IDLE

FILLED WITH

ZEROS

IDLE

CONVERSION

tACQ

A/D STATE

RB1

RB2

RB3

1.5s

Figure 5. 24-Clock External Clock Mode Conversion Timing (MICROWIRE and SPI-Compatible, QSPI-Compatible with fSCLK ≤ 2MHz)

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX1279AETC+

IC ADC 12BIT 1.5MSPS 12-TQFN

MAX1285BESA+T

IC ADC 12BIT 300KSPS 8-SOIC

MAX1302BEUG+

IC ADC 16BIT SRL 115KSPS 24TSSOP

MAX1303BEUP+

IC ADC 16BIT MULT RANGE 20TSSOP

MAX1308ECM+T

IC ADC 12BIT 8CH 4MSPS 48LQFP

MAX1320ECM+T

IC ADC 14BIT 8CH 2MSPS 48LQFP

MAX132EWG+T

IC ADC 18BIT SERIAL 24-SOIC

MAX135EPI+

IC ADC 15BIT PARALLEL 28-DIP

相关代理商/技术参数

MAX1249AMJE

功能描述:模数转换器 - ADC

RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1249BCEE

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1249BCEE+

功能描述:模数转换器 - ADC 10-Bit 4Ch 133ksps 5.25V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1249BCEE+T

功能描述:模数转换器 - ADC 10-Bit 4Ch 133ksps 5.25V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1249BCEE-T

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1249BCPE

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1249BCPE+

功能描述:模数转换器 - ADC 10-Bit 4Ch 133ksps 5.25V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX1249BEEE

功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32